0 引言

近几年来,数据采集的研究工作主要集中在:基于DSP,FPGA等技术的多通道大数据量的并行数据采集[1-2],采样过程中的采样误差及信号完整性分析[3],基于数据频带的滤波处理等等,为探测系统提供了丰富的解决方案。与此同时,石油探测等工业[4]系统针对多变的探测环境,对系统的高速高精度[5]、实时可重配置[6-7]等特性提出了新的具体的需求。

本文采用FPGA控制AD多通道并行采集芯片进行大量数据的采集和处理,深入研究了不同模式下的AD工作时序,设计了可重配置模式、采样频率等的数据采集模块,为可重配置系统的研究提供了参考价值。

1 基于FPGA控制的AD数据采集模块

综合考虑石油探测系统对温度环境等的综合要求,设计方案选择A3P1000作为FPGA 功能芯片,ADS1278作为AD芯片。

A3P1000具有PLL和时钟调节电路,可方便地对输入频率范围在1.5~350 MHz之间的时钟进行控制;拥有32个SRAM 模块,每个SRAM 大小为4 608位,可配置为不同的位数和页数,适合存储多通道高精度数据。ADS1278可并行采集8通道数据;分辨率达到24位;采样频率范围宽,满足一般工业探测系统的频率要求。

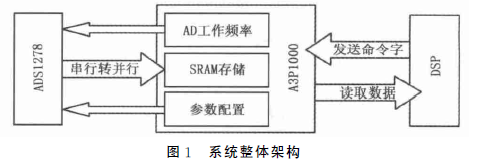

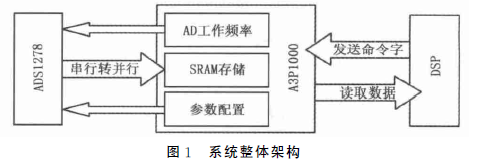

设计系统架构如图1所示。由DSP和上位机系统进行交互[8],获得采集频率、采样点数等一套采集协议命令字。发送成功后,FPGA根据命令字对AD工作参数、存储逻辑进行实时配置,进而获得符合要求的数据结果。

2 AD接口协议控制

ADS1278执行两种数据输出格式和两种串行接口协议。数据输出格式包括:时分复用格式和分立格式。配合FPGA并行处理的特点,选择分立格式:数据由八个通道DOUT1~DOUT8分别输出。

接口协议包括:SPI串行接口和FSYNC串行接口。这两种接口协议在应用过程中对时序有不同的要求,可以根据具体采集目标进行选择。

2.1 SPI协议

SPI是一种只读接口协议,用DRDY信号有效表示数据转换完毕,等待读取。FPGA中的AD控制模块控制串行时钟信号SCLK,自MSB到LSB逐个移出数据,并调用串行转并行的移位寄存器存储数据,转换完成后将数据交给顶层控制模块。

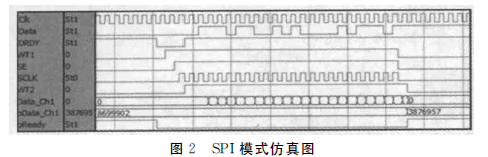

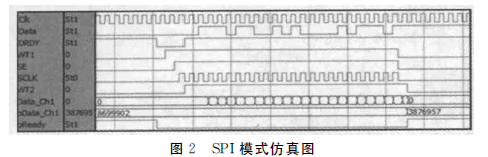

数据的稳定高速采集建立在可靠的时序设计上。SPI模式设计关键点在于DRDY信号、SCLK信号、移位时钟信号的配合。在如图3所示的仿真图中,调用WT1变量识别DRDY信号后第一个CLK信号下降沿;WT1延迟1个CLK信号产生SE,使能SCLK信号;再延迟一个CLK信号产生WT2,使能移位时钟信号。最终实现下降沿采集数据,上升沿存储数据的逻辑,严格避免竞争冒险现象。

在仿真激励文件中按照AD芯片时序规则给出控制信号和一串随机输入数列。可以看到在约24个SCLK之后,oReady信号有效,通知外部接口数据采集完成,并给出稳定的数据信号oData_Ch1。实验中系统可实时响应外部电压信号,给出正确结果。

2.2 FSYNC协议

SPI模式最大的优点在于SCLK时钟可由用户灵活控制,不要求连续运行,为接口开发提供了便捷。但该模式限制了ADS1278只能采用高精度模式,采样频率最高只有27MHz,不能满足石油系统32MHz的采样频率要求。因而对于更高速的采样频率,采用FSYNC接口协议。

FSYNC是一种“从结构”的接口协议。数据的驱动由FPGA提供的FSYNC信号完成。与SPI协议不同的是,该协议要求驱动信号FSYNC和串行时钟信号SCKL必须连续以保证AD芯片的正常运行。

协议的时序限制中要求:从FSYNC信号上升沿到采集有效数据,至少需给出31ns的等待时间。若系统最高工作频率CLK为32MHz,对应一个时钟周期为31.25ns。即等待1个CLK可以满足要求。为了减少多余控制变量,设计SCLK 工作频率为CLK 的1/2。在此基础上,由CLK 驱动状态机转换;由SCLK下降沿驱动FSYNC信号拉低;驱动采集计数器计数;由SCLK上升沿驱动数据存储,完成一个完整的采集和存储周期。

在仿真激励文件中,FSYNC信号触发给出一串随即数列。可以看到:数据转换在一个CLK周期后启动,SCLK 上升沿触发Data_Ch1移位存储,最终将信号放在并行输出信号线上,并给出oReady信号。相比SPI接口,时序限制较多,但设计减少了多余的控制变量,可稳定、正确地采集数据。

3 可重配置采样频率

在实际工业应用系统中,经常需要在连续运行的系统中实时配置采样频率,获得合适频率范围的数据结果。在每一个采样周期内重新配置AD工作频率需要额外的同步时间;而按照最高采样率采样再舍去不需要的数据点则损失了AD性能。需要针对不同的实际系统灵活选择。

3.1 配置AD工作频率

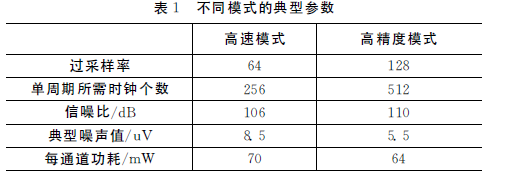

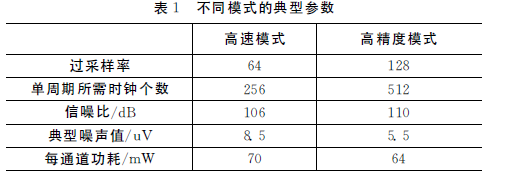

在不同的工作频率下AD性能的差别主要决定于当前的工作模式,即高速模式或高精度模式,优缺点如表1所示。

两种采集模式的临界频率为:高精度模式最高采样频率/高速单周期所需时钟个数×高精度单周期所需时钟个数,为13.5M,换算可得采样周期19μs。为了在每一种采样率下都尽可能发挥最高的系统性能,低于19μs采样周期的采集工作在高速模式下进行,否则使用高精度模式。系统在识别采样频率命令字后对两种工作模式进行切换。

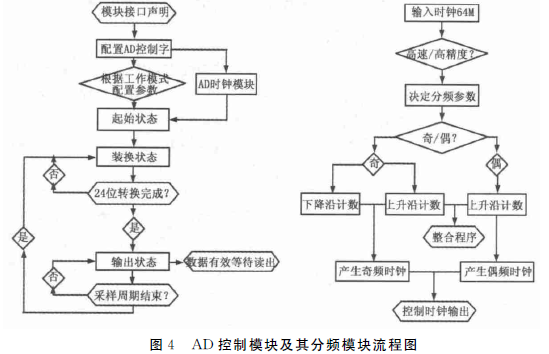

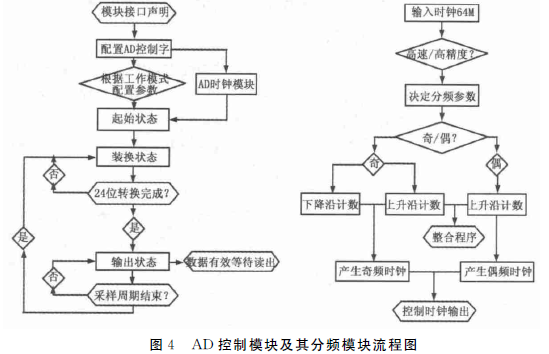

基于此设计思路,对AD工作时钟进行配置。根据FPGA选型A3P1000中的资源限制,不可能简单调用PLL模块生成所有的时钟频率,需要独立模块生成。为了确保CLK 和SCLK的相位一致性,设计中需要用PLL产生一对2∶1的相位“对齐”的基准时钟,同时分别为AD _CLK 和AD _SCLK分频。AD控制模块及其分频模块如图4所示。

程序分为以下几个步骤:

1)控制时钟比。高速模式中控制AD单个采样周期中工作时钟个数为256,而在高精度模式中控制AD单个采样周期中工作时钟个数为512。

2)生成分频系数。在FPGA设计中,一般尽可能避免除法运算,这里直接使用case语句。在进入分频模块后,对选择高速模式的分频系数左移一位,对高精度模式的分频系数不操作。

3)控制相位一致。对奇数倍分频生成时钟时,需要同时对时钟的上升沿、下降沿分别计数并进行相应的处理。那么,就存在同时生成的CLK和SCLK时钟相位差问题,程序设计中通过开关变量对相位进行了控制。

4)奇偶不同的分频倍数生成时钟后统一放在输出信号线上输出。

实际系统可接收预定关键字控制,稳定运行获得采集结果。这种实时配置牺牲了一些逻辑单元资源,最大可能地提高了系统性能。

3.2 基于分频倍数的再采样

在连续运行的系统中,更新AD芯片的工作频率需要重新进行同步,同步时间为128个数据点周期,在较低速的采样频率下可能为采集周期增加了较可观的准备时长;另一种情况下,外部噪声已经淹没了高精度模式所能带来的有效位数提高。那么,上述设计不为可取。

因此提出另一种方案。控制系统按照基准采样率恒定工作。对于采样周期为基准周期N 倍的命令字需求,则AD每采集N 个数据再进行存储。实质上起到了再采样的作用。从理论上分析,除了AD工作模式所带来的硬件性能差异,不会对波形造成任何影响。这种方案略微牺牲了系统的性能,但大大简化了逻辑处理并减少了部分关键信号的扇出系数,并省去了更改AD工作频率时的同步时间。

4 实验结果以及系统性能分析

下面通过实际测试评估AD工作的性能:将八路模拟电压输入信号端直接短接至AD参考电压VCOM,采集600组数据后由DSP读出交给上位机。最后,由Matlab软件统计数据的相关参数。针对每种采样频率,每种模式分别做10次采集实验。采样频率命令字的发送包括以下3种情况:稳定连续采集,重配置后首周期发送,重上电后首周期发送。对10次采集下的8通道数据取平均值进行分析,具有代表性。

芯片在典型噪声、最大噪声和不同采样周期下实际采样结果有效位数值如表2所示。由于整个系统处于实验室测试环境中,环境噪声超过AD芯片本身的噪声,整体精度有所降低,属正常情况。

系统能够在连续运行过程中,实时接收采样频率控制命令字,扩大了可以采集的频率范围,便于后期的数据分析。实验给出了两种方案的有效位数。可以明显地观察到:在高精度模式下,系统的性能得到了1位左右的有效位数提升。通过示波器对采样时间的观察可以看到,在高速模式下采样周期更短。两种需求侧重不同的方案为工业测试提供了更多的选择。

5 结论

随着系统架构的改进、芯片精度的提高,数据采集模块的性能也越来越好。在此基础上,灵活地配置和设计数据采集的工作模式、频率等无疑拓展了采集系统的应用范围和使用寿命,在无附加成本的基础上提高了系统性能,是工业应用中值得借鉴的设计方法。

张 燕1,黄 伟2,叶朝辉1,肖 冰3,刘西恩3

(1.清华大学自动化系,北京 100084;2.北京睿清智华信息技术有限公司,北京 100084;3.中海油田服务股份有限公司,北京 100084)