摘要:介绍了一种基于PCI 总线的雷达数据采集及定时板的设计方案,该设计把数据采集控制、发射机定时及接收机控制等集于一块FPGA 芯片中实现,具有设计简单,可靠性高等优点。该设计已经成功地应用到民航飞行天气探测领域中。

在现代雷达系统中,雷达信号处理部分一般由数字中频、DSP 信号处理器、雷达定时及计算机显示等部分组成,其中DSP 信号处理器是雷达数字信号处理及运算的核心部分,也是技术难度较大、价格较高的一部分。随着计算机和IC 技术的发展,在现代雷达系统中,雷达信号处理部分中的DSP 信号处理器用高性能PC 机来代替其运算功能已经成为了可能,这不但从根本上改变了信号处理的设计思想,同时也使得雷达信号处理的硬件简化成数字中频、数据采集及定时、计算机处理及显示3 大部分组成,大大简化了雷达信号处理部分的设计难度,降低了系统的成本。

1 数据采集及定时方案分析

在本雷达系统设计中,雷达的数字中频、数据采集及定时、信号处理分成了3 个独立的模块。雷达回波数据在数字中频模块中经过高速采样、下变频、缓存,数据速度已经降为2.4Mbps(l、Q 数据各24 位)。数据采集的目标即把这

2 .4Mbps 的I 和Q 数据,在定时信号的严格同步下,准确地通过PCI 总线传输到计算机中;同时,由PC 机往FPGA 的定时配置空间写入不同的定时参数,以此产生整个雷达系统的发射机和接收机的定时与控制信号。方案的设计主要考虑到雷达数据采集的距离分辨率、实时采集及定时信号产生与接口传送。鉴于数据速度并不很高,方案中选用了两片18 位的FIFO 芯片CY7C4265 共同构成24位、深度为16阔的数据缓存;与计算机总线的接口采用32位的PCI 总线接口芯片PLX9054。总线接口逻辑、FIFO 控制逻辑及定时与控制信号皆由一块FPGA 芯片ACEXIK50-208实现。在系统程序结构中,尽量使程序都模块化、参数化,以便提高模块的通用性、移植性和易扩展性。

2 雷达数据采集及定时工作流程

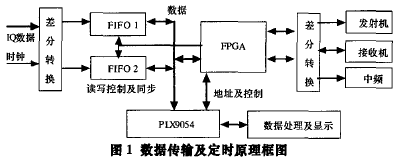

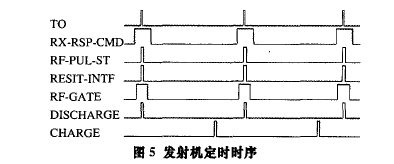

本数据采集及定时板是整个雷达系统的核心部件之一,系统的主同步信号TO、距离库参数、系统工作模式、接收机控制、发射机定时等都由其得到和产生;与此同时,回波的I 和Q 数据也由其传输到计算机进行各种处理。系统流程框图如图l 所示。

脉冲雷达的数据采集并不是随机的,而是要求与系统主同步信号严格同步。在本雷达系统中,系统主同步信号TO是由FPGA 芯片根据定时参数产生的。定时参数是由用户依雷达工作模式通过Windows 应用程序写入FPGA 配置空间的,其中参数中的距离库决定了每帧数据的数量及时间,即由主机间步信号TO 控制何时开始采集数据,距离库参数控制每帧需要采集多少数据及每次计算机需要从FIFO 中读入的数据量;与数据有关的参数,还有雷达的工作模式,如在批处理模式中,窄脉冲和宽脉冲下的I、Q 数据量是不一样的。而对于雷达来说,回被数据传输的准确性是至关重要的,因此,在设计过程中,要特别注意回波数据质量及数量的严格准确。

发射机和接收机的定时参数,一般是在雷达系统运行前进行初始化,然后由FPGA 的复杂逻辑产生。如果运行期间改变模式,程序中处理先停止当前工作模式,待新参数写入后重新产生新的定时和控制信号。考虑到信号传输线长,容易被衰减和干扰,通常采用差分线传输。由上可知,在此数据采集及定时板卡设计中, FPGA 及PCI 总线起了举足轻重的作用。下面就以FPGA 及PCI 总线的设计,详细叙述实现原理及过程。

3 数据采集及定时的实现

3.1 PLX9054 局部总线时序

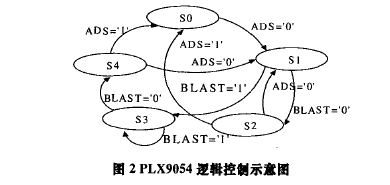

PLX9054 是PLX 公司推出的一款32 位PCI 总线接口芯片,工作模式分为M 、J、C3 种,本设计主要采用C 模式。对于PLX90日,除了PCI 总线信号外,用户在设计时需要用到的信号主要是局部总线的数据、地址及控制信号3 大类,而在三者之中,控制信号是设计的重点,包括ADS , BLAST,READY, LWRJRD, LHOLD, HOLD 等信号,实现功能主要为单数据访问、突发式访问及DMA。为了利于PCI 模块的扩展和灵活使用,本设计中采用了状态机来实现PLX9054 模块的局部总线时序,状态机如图2 所示。状态机的时钟为局部总线时钟LCLK ,在PLX9054 读写操作时,如果ADS 为低就表示数据操作开始, BLAST 为低表示正在传输最后一个数据,即本次操作结束;如果BLAST 一直为高,则表示数据仍在传送。图2 中状态机SO , SI , S2 , SO 循环是实现单数据操作, SO , S 1 , S4 , SO 实现PCI 总线突发模式数据操作(包括DMA)o READY 信号在ADS 为低后有效,表示设备准备好,状态机S2 和S5 变为无效。为了易于程序设计,局部总线时序单独成模块,状态机直接作为端口输出,后面的模块只要根据状态机直接对信号进行相应变化就行,而并不需要对PLX9054 接口很熟悉。

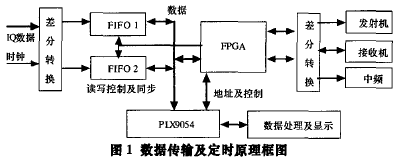

3.2 用FPGA 实现FIFO 控制

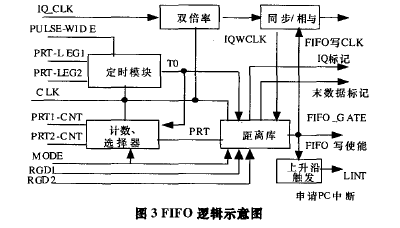

雷达回波数据在传输到计算机之前,首先在FIFO 中进行打包,包的大小及占用时间与雷达系统定时有关。如图3所示, PRT-LEGl 和PR下LEG2 为雷达重复频率参数,其决定系统主同步信号TO 的周期;RGDl和RGD2 分别为距离库参数,其决定雷达的探测距离; PRT1 -CNT 和PRT2-CNT 分别表示窄脉冲和宽脉冲的个数; PULSE-WIDE 和MODE 则说明雷达的宽窄脉冲和工作模式。雷达在连续警戒模式和多谱勒模式下,主同步信号TO 及FIFO-GATE 信号只与PRT-LEGl , RGDl 及RGD2 有关。如果是MODE= ‘ 1 ' ,批处理模式下,则与PRT-LEGl , PRT-LEG2 , PRT1 -CNT 、PRT2-CNT、RGDl 及RGD2 参数都有关。

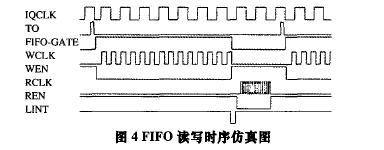

由于FIFO 写控制逻辑涉及参数和约束条件较多,实现复杂,也很容易出错。因此,在设计时,首先应对TO 信号调试仿真,以保证主同步的准确。其次,在根据距离库计算I、Q 数据量时,应同时考虑到与TO 信号及IQ_CLK 的同步,信号仿真时序如图4 所示。

由于雷达中频I 和Q 数据是在IQ_CLK 的上升沿和下降沿分别有效的,而FIFO 数据写入都是在时钟上升沿有效,因此,在FPGA 中设计了一个双倍率模块, IQ_CLK 经此模块后相当于进行了倍频。FIFO 数据帧读操作是在计算机响应中断后发起的,采用DMA 方式。

3.3 霄达定时信号实现

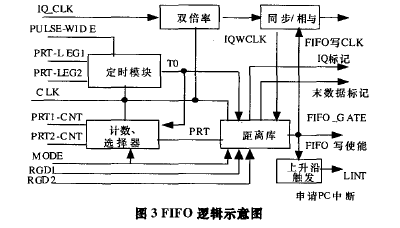

本板卡为发射机主要提供4 种定时信号:充电定时信号CHARGE ,放电定时信号DISCHARGE ,抗干扰定时信号RESIST_INTF 及高频定时信号RF]LS_ST。其中充电定时信号决定了发射机每个周期回扫充电的起始时刻和重复频率;放电定时信号决定每个调制脉冲的起始时刻及调制脉冲的重复周期;抗干扰定时信号触发一个发射机的抗干扰脉冲;高频定时信号则决定了一个发射机输出高频脉冲的起始时刻,并且高频定时信号的重复周期决定了发射机输出高频脉冲的重复周期。4 种发射机时序关系及约束较多,实现逻辑较复杂,这里不再多述,仿真时序如图5 所示。与发射机定时相关的参数,在雷达系统运行前由计算机统一进行初始化。

4 结束语

雷达数据采集及定时是雷达系统中核心部件之一,它的好坏直接影响到整个雷达系统的运行。本文介绍了一种基于PCI 总线的雷达数据采集及定时板的设计方案,并对其关键技术要点作了详细的叙述。目前,本设计已经成功地应用到民航飞行天气探测领域中,并取得了良好的效果。