孟会,刘雪峰

(解放军信息工程大学电子技术学院,郑州450004)

摘要:无论在计算机内部还是外部,统一的总线标准和提高总线带宽已是当务之急,从技术的角度分析了PCI Express 总线的技术特点、系统架构、体系结构及其物理结构与接口规范,对其发展前景给出了评估与预测。

关键词PCI Express 总线;技术分析;发展前景

PCI 总线技有自20 世纪90 年代初期开始应用至今已14年,其间没有根本性的发展,而处理器却在每个摩尔周期中,性能就提高一倍。技术发展上的不同步,使PCI 总线逐渐成为整个系统的瓶颈。虽然PCI 总线技术至今仍是主流,但就其本质而言,它早已不能适应了。高性能的图形芯片在7 年前就第一个从PCI 总线中分离出来,形成单独一种总线技术一-AGP。随着RAID 阵列、千兆位以太网和其他高带宽设备在消费级系统上的出现, PCI 的带宽明显不能满足这些应用的需要,不能随着主频的提高或电压的降低而灵活调整传输速率,同步时钟数据传输受单一上升沿限制,信号路由规则受FR4 技术、接口引脚过多等的制约,所有这些限制都建立一个更高带宽、通用的1/0 总线。

芯片组制造商已预见到这些限制所带来的问题,对主板芯片组作了一系列改进以减轻PCI 总线的负担。Intel 自800系列芯片组开始采用HubLink 连接技术, AMD 的芯片组阅采用Hyper Transport 技术, VIA 和SiS 芯片组南北桥间分别采用各自的Via-Link 和MuTIOL 芯片连接技术。20 世纪90年代后期,出现了PCI-X 新总线标准。系统内部南、北桥芯片间的总线技术也绕过PCI 采用其它总线技术。外设接口方面早已不再采用PCI 总线,在芯片组南桥中都基本集成了EIDE, USB 和IOMI1 00MBps 以太网接口。

PCI Express 的前身就是著名的3GIO(3rd GenerationInputlOutput) ,研发代号为Arapahoe 。由Intel、Dell 、Compaq 、IBM、Microsoft 等PCI SIG( PCI Special Interest Group)联合成立的Arapahoe Work Group 共同草拟并推举出取代PCI 总线标准的新一代标准。高性能、高扩展性、高可靠性、更良好的升级性以及更为低廉的花费,就是PCI Express 的设计理念。

1 PCI Express 的技术特点

PCI Express 具有鲜明的技术优势和特点,它全面解决了PCI 总线技术所面临的种种问题,迅速得到业界的承认,被公认为下一个10 年的总线标准。PCI Express 的设计不只要取代PCI 及AGP 的插槽,同时也是一些电脑内部系统连接接口。它不但可被用在台式机、笔记本电脑以及服务器平台上,甚至会延伸到网络设备的内部连接设计中。其关键技术特点如下:

(1)设备间高速串行点对点传输。PCI Express 总线采用点对点技术,为每块设备分配独享通道带宽,不在设备之间共享资源,充分保障了各设备的宽带资源,提高了数据传输速率。

(2)双通道、高带宽、传输速度快。PCI Express 总线采用独特的双通道数据传输模式,大大提高了数据传输速度。PCIExpress 从每个信道单向2.5Gbps 的传输速率起,在物理层上具有的1-32 速可选信道带宽特性,使其轻松实现"无限"的扩展传输能力。

(3)灵活的扩展性。PCI Express 总线能够延伸到系统之外,采用专用线缆可将各种外设直接与系统内的PCI Express总线连接在一起。

(4) 低功耗及电源管理功能。单通道带宽模式的PCIExpress 总线接口插槽是18 针引脚。实际上每个通道只需4根线,发送和接收数据的信号线各一根,各一根独立的地线。其余的14 针都是通过4 根芯线相互组合得到的。减少了数据传输线数量,电源消耗大大降低。

(5)支持设备热拨插和热交换。PCI Express 总线接口插槽中有热拨插检测信号,可像USB 、IEEE 1394 总线那样进行热拨插和热交换。

(6)支持QoS 链接配置和公证策略。

(7)支持同步数据传输。

(8)封包分层协议架构。

(9) 多点虚拟通道技术。PCI Express 总线技术在每一个物理通道支持多点虚拟通道,每一个单物理通道允许有8 条虚拟通道进行独立通信控制,每个通信的数据包都定义不同的QoS 。

(1 0)可保持端对端和链接级数据完整性。

(1 1)具有PCI 级的错误处理和先进的错误报告功能。

(1 2)小型连接,节约空间,减少串扰。与PCI 相比, PCIExpress 总线在主板上的导线数量减少了75% ,速度快且数据不需同步。主板上走线少、间隔宽、串扰影响不明显。

(1 3)在软件层兼容PCI 标准(非硬件和接口层面)。跨平台兼容是PCI Express 总线非常重要的一个特点。PCI 2.2 设备可在它提供的低带宽模式下运行,为用户提供了一个平滑的升级平台。PCI Express 标准中也PCI-X 接口标准兼容,但它不兼容目前的AGP 接口。

2 PCI Express 系统架构

PCI Express 是一种高性能、高灵活性、高可扩展性、稳定可靠的低成本通用1/0 架构,它融合多个市场领域的所有应用要求,以无缝的方式弥补了现有PCI 总线的不足并进行市场过渡,使设计人员能够逐步采用新的拓扑技术。与共享、并行总线体系的PCI 相比,点对点传输允许每个设备都拥有专属的一条连接,不争夺带宽资源,这一点是重大突破。PCIExpress 可以作为主板的一部分不会和诸如USB 2.0 、InfiniB and 以及Ethernet 等发生冲突。

2.1 PCI Express 系统基本架构

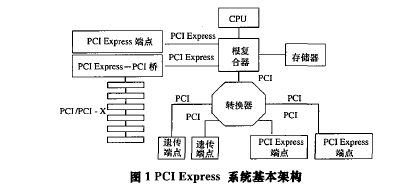

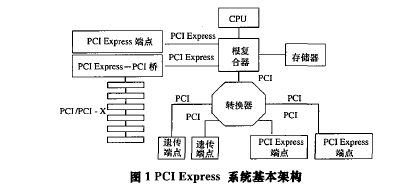

PCI Express 系统基本架构如图10

以PCI Express 为网络的标准系统是由设备之间的点对点连接组成的。基本的PCI Express 系统是由一个根复合器(功能上类似于北桥芯片)、转换器(软件包含多个PCI-to-PCI 桥,以保证兼容性)以及不同的终端设备,也包含类似于PCI 转PCI Express 的桥接设备。点对点传输可以让一个终端设备通过根复合器将数据传送到另一个终端设备,或者从一个终端设备经过一个转换器到另一个转换器,然后再到另一个终端设备。另一种方式称之为高级点对点传输,附加的功能可以实现未来的"PCI Express 高级信息包转换器飞一个根复合器通过高级转换功能来实现主机软件之间的点对点传输。

2.2 PCI Express 物理串行连接特性

基本的PCI Express 串行连接使用两组独立低电压差分驱动信号的全双工接口:收发各一组(4 根电缆)。相当于两个独立的单向接口,每个方向的电缆都有各自的接地线,同时进行数据传输,这样就获得更高的速度及更好的信号质量。关键的设计是在4 层PCB 技术及标准的接口上,允许20 英寸的连接长度。若采用质量更高的元件,传输距离将更远。和并行线缆连接相比, PCI Express 具有更好的抗电磁干扰特性。因为电缆有良好的屏蔽性,可以利用缠绕来降低电容值,串行信号能传输很长的距离。总线宽度只是前者的114 。从主板上的信号传输来看,由于PCI Express 减少大量的点对点线路,可以抵抗在并行总线架构中经常出现的信号干扰、信号失真以及其它电子信号的缺损问题。在进行长距离传输以及接口传输时, PCI Express 的设计也必须完善差分信号传输损失的问题。PCI Express 串行连接的另一关键特性是通过8b/l0b 编码来嵌入时钟信号技术。时钟信息被直接编码到数据流中,而非以单独的信号存在。尽管串行数据/时钟信号流比单独时钟信号的并行数据总线传输更长的距离,价格也相对低廉,内置I10 设备也有更好的数据传输。但8bl1 0b 编码每个字符需要lObits ,占用20% 的通道,提取和嵌入时钟信号需要附加的处理时间,在需要更低延迟的高速多处理器系统中,并行界面还会存在一段时间。

2.3 PCI Express 串行连接结构

PCI Express 连接包含多个管线。每个管线包含基本连接的收发两组差分驱动电缆,子连接依靠现有的2.5Gbps 达到lOGbps 。多重子连接可连接设备以及芯片等。表面上和利用多重管线的并行界面相当相似,实际上是一组独立的串行连接,不像并行界面那样容易受到信号干扰。PCI Express 的管线位宽可以为xl 、x2、x4、x8 、x12、x16 以及x32 等不同形式。一个xl 连接有4 根线,一个x16 有双向传输数据的电缆。高端领域,一个x32 单向连接能够传输80Gbps 。由于8b/l Ob编码嵌入时钟信号占用20% 的管线带宽,实用带宽约为64Gbpso PCI Express 连接为对称结构,两边的管线必须相等。管线的先后次序可在每个设备中进行交换,差分信号的正负两极可翻转,这样的设计更为灵活,避免布线时的物理信号交叉。来自程序的数据流可通过多重管线的PCI Express 进行传输,数据流在经过多重管线时可拆分并被发送到不同的管

线,并在接收端进行数据流重组,简化操作,提高效率。

3 PCI Express 的体系结构PCI Express 体系结构采用封包分层协议结构,不需在主串连接上加入任何边频信号,协议中允许两个不同的功能区之间进行隔离,一个层内的数据传输和其它层无关,有利于踌平台应用。PCI Express 的体系结构兼容PCI 地址结构模式,所有已有应用和驱动程序均不需作任何修改即可应用到新总线系统中。PCI Express 配置使用标准的PCI 即插即用规格标准。PCI Express 体系结构分为4层,从下到上依次为物理层、数据链路层、处理层和软件层。从一个设备传输数据到另一个设备时,每个设备都被看作是一个协议堆擒。数据传送从处理层发起,数据包在高层上生成,每传递到一个低层就添加一些信息,直到它通过物理层发送到接收设备,从接收设备到协议堆核再上传,直到被程序接收(如图2 所示)。

(1)物理层:物理层是最低层,它负责接口或者设备之间的链接,是物理接口之间的连接,它决定了PCI Express 总线接口的物理特性。PCI Express 支持两种类型的中断,现行的PCIINTx 和信息信号中断(Message Signaled Interrupt, MSI) ,MSI 中断可以进一步优化PCI2.2/2.3 设备。INTx 中断可用信号方式中断主机芯片的请求,与现行的PCI 总线的驱动程序和操作系统兼容。MSI 中断是通过内存写处理操作,边沿触发和发送的。重新编写驱动程序对于MSI 边沿触发中断是非常有利的,在数据包协议中通过串行链接使用MSI ,是一种行之有效的本地中断方式。MSI 在多处理器系统中任何设备都可发送中断,比主机直接发送中断更加有效。

(2)数据链路层:数据链路层的任务是确保数据包的可靠、正确、完整,并在数据包中添加序列号,发送16 位CRC到处理层。大多数数据包是由处理层发起的,基于信任,数据梳控制协议确保数据包只在终端缓存空闲时传输。对所有重试的数据进行排队,使得信道带宽浪费现象得到有效的控制。数据链路层在信号中断时自动重新传输数据包。

(3)处理层:处理层接收从软件层送来的读、写请求,并建立一个请求包传输到数据链路层。所有请求分离执行。处理层同时接收从数据链路层传来的响应包,并与原始的软件请求关联。处理层还整合或拆分数据包来发送请求,如数据读、写请求,并操纵链接配置和信号控制,确保端与端之间连接通信的正确性,没有无效数据通过整个组织。处理层使用基于信任的流控制机制来确保接收设备有足够的缓存资源用于接收发送端设备传输的数据大小和类型。

在PCI Express 总线技术中,数据包主要是处理层数据包(Transaction Layer Packet, TLP) 和数据链路层数据包(DataLink Layer Packet, DLLP) 。每个数据包都有一个使响应包定向于正确发起者的唯一标识符,包格式支持32 位内存地址和扩展64 位内存地址,并有非窥探、无严格排序和优先权等属性,用于优化路由I10 子系统的数据包。数据包头包括许多控制信息和端到端传输数据,端到端的数据传输中使用32位冗余校验码。每一个处理根据数据包的传输等级性质进行不同的处理,每个数据包都定义不同的QoS 。当数据包通过PCI Express 组织传输时,数据包的基本传输信息和传输策略得在每个交换器或者链接终端到应用。处理层包括4 个地址空间: PCI 接口原有的内存, I10 地址空间,配置地址空间, PCI-Express 接口新加的信息空间。这里特殊规格格式的内存写代替无边信号硬写。

(4)软件层:软件层是最重要的部分,它是保持与PCI 总线兼容的关键。其目的在于使系统在使用PCI Express 启动时,像在PCI 下的初始化和运行一样,无论是在系统中发现的硬件设备,还是在系统中的资源,不需要任何改动创建非常优化的系统环境。在PCI Express 体系结构中保持这些配置空间和νo 设备连接的规范稳定是非常关键的。在PCIExpress 平台中所有操作系统在引导时都不需要进行任何编辑,也就是说在软件方面完全可以实现从PCI 总线平稳过渡。在软件响应时间模式方面, PCI Express 体系结构支持PCI 的本地存储、共享内存模式,所有PCI 软件在PCI Express 体系中运行都不需作任何改变。当然新的软件可能包括新的特性。软件层的另一重要功能是进行错误处理和提供错误报告。

4 PCI Express 的物理结掬与接口规范

4.1 PCI Express 的物理结构

PCI Express 接口是完全独立于PCI 总线的全新总线结构。它不同于PCI 结构,原来的PCI 设备不能插在PCI Express新接口中,为保持与原有总线系统结构兼容,在将来的主板上必须留有一定的PCI 插槽。PCI SIG 已完成PCI Express 技术新规格的制定工作,新规格PCI Express Mini Card 是将PCIExpress 技术面向移动平台扩展而成。该规格有望成为目前实际应用于移动终端的Mini PCI 规格的后续规格,它补充了PCI Express Card 的要素,并有望应用于按照移动终端的BTO(按单定制)及CTO(按单配制)商业模式生产的有线及无线外设。

4.2 PCI Express 物理接口规范

下面以台式机的Xl 带宽模式下的PCI Express 插槽接口物理结构中各针脚定义为例,说明PCI Express 物理接口规范。xl 模式下的插槽针脚定义如表l 所示。

其它带宽模式下和Xl 带宽模式下的PCI Express 总线接口插槽主要区别在于信道的多少,而主要控制功能是在O 号信道的模式下,其它模式下的插槽是在O 号信道基础上附加一些发送和接收差分信号对连接及相应的地线。

5 PCI Express 的发展前景

尽管PCI Express 具有许多的技术优势,但在PCI Express出现前后也有其它的总线技术作为PCI Express 的竞争者出现。主要有PCI-X、HyperTransporto PCI-X 技术是目前PCI技术的延伸,只加宽了总线的宽度而已,没有根本性的改变。HyperTransport 是AMD 公司的技术。从技术而言,HyperTransport 和PCI Express 有不少相似之处,使人不自觉地将它们相提并论。其实从定位来看, PCI Express 的服务对象更多的是电脑设备, HyperTransport 则成为高端网络设备的一个高带宽的解决方案。这使它们的可比性也大为降低。后来, Hyp巳rTransport 的创作者AMD 也加入了PCI SIG 中,成为了PCI Express 中一个关键合作伙伴。

随着ATI、NVIDIA、INTEL3 个巨头的认同和加入, PCIExpress 的前景一片光明。业界头号接口产品供应商TI 一如既往地支持PCI Express ,并保持市场领先地位,这为PCIExpress 提供了强大的后盾。基于PCI Express 的主板已经上市,多家公司的多种基于PCI Express 的显卡面世, Intel 公司正研制基于PCI Express 的网卡和通用接口芯片, IDT 公司推出了4 款由桥接和转换产品组成的PRECISE 系列PCIExpress 产品, Xilinx 公司制造了支持PCI Express 的集成622Mbps- 1O .3125Gbps 串行收发器的Virtex-4 FX60 90nmFPGA 。可见在国外对于PCI Express 的研发已经全面地展开,PCI Express 替代PCI 势在必行。

6 结束语

众多产品的支持会令PCI 总线的寿命延长,但PCIExpress 即将改变整个计算机系统结构、成为下一代总线标准的总线技术。在其应用方面,本文已经做了相关研究,下一步的工作是利用FPGA 快速地实现PCI Express 应用。