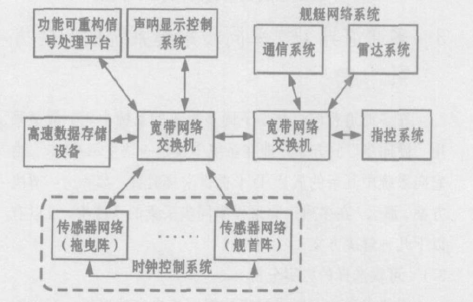

网络中心战系统利用强大的计算机信息网络, 将分布在广阔区域内的各种传感器, 指挥中心和各种武器系统合成为一个统一高效的大系统, 实现战场态势和信息的共享。

传感器网络是整个网络中心战系统的最基础部分[2 ]。A /D数据同步采集包括的主要内容是将整个网络中的传感器信号由模拟转换为数字, 这种转换应使各个通道数据的相位一致性在一定的误差范围内。本文的研究工作立足于上述网络中心战系统, 研究了多通道信号异采样率同步数据采集的问题, 并提出了一种解决方案。

图1 舰艇上网络中心战系统

2 多通道异采样率信号同步采集系统模型

在网络中心战系统中,各种型号的声呐协同工作,而不同型号的声呐用途不一, 参数也各异, 就整个大系统而言,是一个多通道组成的以不同采样率进行工作的系统。

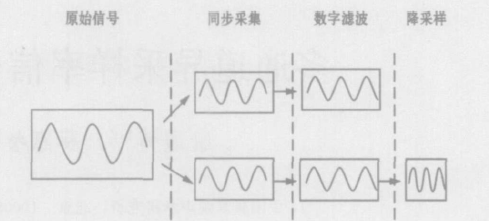

图2 多通道异采样率系统模型

图2是一个多通道异采样率的系统模型。图中的多路传感器是由多种声呐组成的传感器阵列, 它们可能会有不同的特性, 实现不同的功能, 满足不同的需求。传感器的信号送至多通道A /D信号采集卡, 信号采集卡在统一时钟控制下, 根据各自的需求对系统统一时钟进行时钟变换, 以满足自己的采样率需求。信号经过A /D采集卡后变成数字信号送至数据传输模块, 经过数据融合后传送至千兆以太网交换机, 由此,专用的信号处理设备就可以从网络上获取所需要的数据, 再根据规定的算法对数据进行相应的处理。

这种模型的优势在于:

( 1) 可以方便各声呐子系统共享数据和控制信息。

( 2) 可以对多部声呐系统进行集中处理。

( 3) 可以对电子设备互为备份系统冗余性强。

( 4) 支持系统功能动态重构和性能升级。

( 5) 减少系统的连线数量提高系统可靠性。

3 多通道异采样率同步采集系统的解决方案

在多通道相同采样率下同步采集的系统中, 一般是采用“硬同步” 的方式, 即在系统中设定一块主A /D卡, 由它向系统中其余的从A /D卡提供采样时钟。参考这一解决方案, 那么, 在多通道异采样率同步采集的系统中, 可以有以下几种解决方案。

3. 1 可供选择的方案分析

围绕多通道不同采样率数据同步采集的思想, 有以下几种方案可供选择:

( 1) 同步采集, 数字滤波, 降采样这种解决方案的步骤如图3所示。其过程基于多通道相同采样率信号同步采集的思想, 是对原始信号以“主-从” 方式进行同步采集,然后对需要降低采样率的通道进行数字滤波, 最后对滤波后的信号进行降采样。

图3 多通道异采样率同步采集解决方案一

中间有一个环节是数字滤波所必须的。为什么需要降采样的通道在降采样之前需要对其进行滤波? 因为该通道是以高采样率进行数据采集的, 在采样后的信号里可能会混杂了其它高频的信号, 这些信号如果未经滤波就进行降采样的话, 就会在信号里混入某种可能并不存在的信号成分。

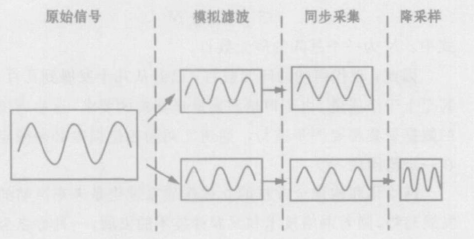

( 2) 模拟滤波, 同步采集, 降采样

这种解决方案的步骤如图4所示。其思想跟( 1) 方案中的思想类似, 不同之处在于将同步采集环节和滤波环节互换了一下,将原来的数字滤波改用硬件电路来实现; 在模拟滤波后, 再对滤波后的模拟信号以“主- 从” 方式进行同步采集, 同步采集后, 对获得的数字信号直接进行降采样。

图4 多通道异采样率同步采集解决方案二

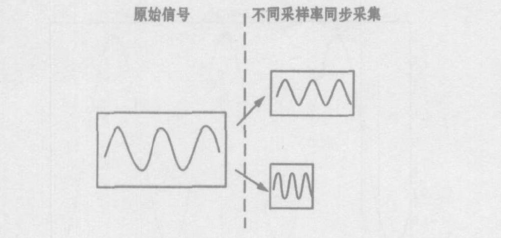

( 3) 利用同一时钟驱动, 设置不同的采样率进行采样

这种解决方案的步骤如图5所示。这种方案的思想跟前两种方案有很大的不同。首先,它借鉴了多通道相同采样率信号同步采集的思想, 也是采用“主- 从” 的工作方式, 一般是将主卡设置为高采样率的卡, 主卡将采样时钟送给系统其余的A /D卡, 需要以低采样率进行采样的A /D卡在接收到主卡的时钟后,在FPGA里对时钟进行分频处理,来满足自身的采样需求。

3. 2 三种采样方案的比较

第一种方案的特点是实现比较容易, 数字信号的相位一致性好,缺点是需要专门的DSP来实现滤波算法,在系统通道数量较多和采样率较大的情况下, 需要比较多的硬件

资源来完成。

图5 多通道异采样率同步采集解决方案三

第二种方案的特点是增加硬件电路代替数字滤波环节来完成滤波过程。这样做的好处是对数字电路部分的DSP运算能力要求大为降低, 也不再需要设计滤波算法; 缺点是增加了硬件成本, 从而增加了系统的体积和重量,并且效果没有数字滤波的效果好。

第三种方案不需要额外的滤波环节, 因为A /D采样芯片会自动地进行这个过程。在该方案中采用的是ΔA/D转换芯片[5] , 能根据采样率设置系统A/D转换的截止频率。

这种方案的特点是实现的思想简单直接, 既不像方案( 1) 需要专门的DSP来进行数字滤波, 也不像方案( 2) 需要专门的硬件来实现模拟信号滤波, 它仅需要在FPGA的逻辑里进行一些特殊处理, 即可实现在同一系统中的同一时钟下以不同的采样率进行同步信号采集。这种方案既能降低硬件成本, 不增加系统的复杂性。

4 多通道在同一时钟信号下分频采集

如上述方案三, 在一个多通道数据采集系统中,如果某些不同的通道需要以不同的采样率进行同步数据采集的时候, 使用主从结构, 系统中各个通道在主A /D卡时钟的驱动下, 再根据各自的采样率需要进行分频处理,不失为多通道异采样率同步采集系统的一种不错的解决方案。

4. 1 A /D数据采集卡的结构和工作原理

要实现一个系统中的所有A /D数据采集卡在同一时钟驱动下进行数据采集, 那么在这个系统中的所有A/D数据采集卡必须采用“主- 从” 结构设计。作为主卡的A/D数据采集卡产生时钟信号, 给包括自身在内的系统中的所有A /D数据采集卡使用。这样, A /D数据采集卡上有如下设计:

· 跳线装置, 设置该A /D数据采集卡是工作在主模式还是从模式;

· 在A /D数据采集卡上需要有时钟输入输出接口;

· 有可编程的逻辑器件如FPGA对时钟进行控制;

· 更进一步的有DSP进行数据流的控制和传输。

图6 A /D数据采集板结构图

多块A/D数据采集卡组成系统的工作原理是这样的:

将处于中间位置的A /D数据采集卡通过跳线设置为主卡, 其余的A/D数据采集卡设置为从卡;

用同步线(时钟和控制连线) 将系统中所有A /D数据采集卡连接起来;

对需要以不同采样率进行采样的A /D数据采集卡的逻辑芯片中(一般是FPGA) , 加入相应的分频逻辑;

在驱动控制程序里进行对数据同步采样进行控制。

4. 2 同步控制

A /D数据采集卡上的DSP用于对数据采集过程进行控制和对所采集的数据进行缓冲。A/D芯片采样率的设置、A /D数据采集卡上的增益控制都是通过运行在DSP上的程序来完成的, 见图6。

系统中的每块A /D数据采集卡通过加载驱动程序来运行。对于系统而言, 由于系统是数据驱动的, 而数据又是在时钟的驱动下获得的。所以, 系统先加载从A /D数据采集卡的程序, 让从A /D数据采集卡处于就绪状态后, 再加载主A /D数据采集卡的程序, 此时, 主A /D数据采集卡同时给自身和系统中的其余从A/D数据采集卡提供时钟, 整个系统就可以进行同步数据采集了。

然而, 仅仅这样还是不够的。根据文献[5] , A /D采样芯片在开始正常工作前需要有一个校正的过程, 并且在不同的采样率下其校正时间并不一致。这样就会造成不同采样率下不同的通道采样数据无法对齐, 从而对通道间的相位一致性问题带来严重的影响。

所以, 在系统的同步控制中要加入统一的开中断信号,在所有的A/D数据采集卡都校正完毕进行正常的数据采集了之后, 由主A /D数据采集卡发出开中断指令, 这样才能达到系统中所有的A /D数据采集卡完全同步采集。

此外, 由于不同的通道采样率不一致, 在ΔE采样芯片中对信号的截止频率也会不一样, 换言之, 就是在A /D芯片中的低通滤波器参数不一致, 这样就不可避免的造成不同的采样率通道的有不同的相移。因此,应该将采样率高的那些通道中的数据右移一段位置, 来保证所有通道的数据对齐。

5 试验结论和进一步研究

5. 1 试验结论

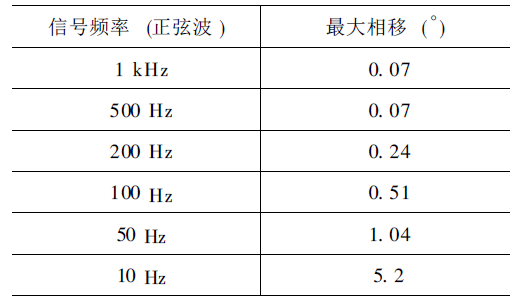

上述研究成果已经成功地应用在某声呐系统中。该系统由65个通道组成, 同时有100 k Hz和50 k Hz两种不同的采样率。试验结果表明, 当信号频率在100 Hz以上时, 系统各个通道之间( 100 k Hz和50 k Hz采样率的通道之间) 的相位误差在0. 6°以内, 在50H z时, 其相位误差约为1°。如表1所示。

表1 通道间相位一致性测试

5. 2 进一步研究的问题

( 1) 低频相移问题

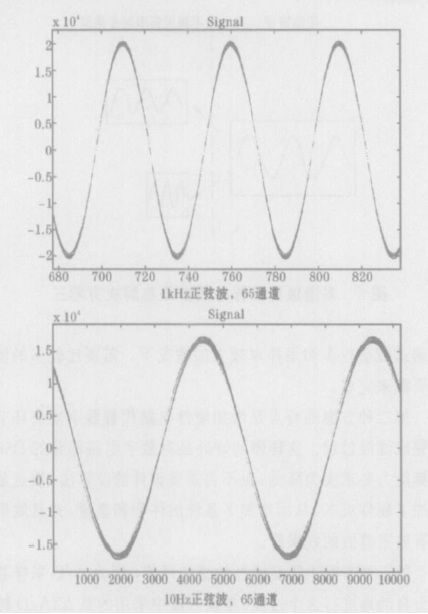

如表1中所示, 当信号频率在10~ 100 Hz之间时, 100k Hz采样频率的信号相对于50 kHz采样频率的信号相位有比较明显的偏移, 具体表现为:从图7中不同正弦波下各个通道的波形图比较中可以看到, 在10 Hz下, 通道间的相位有比较明显的偏移, 图8是其中10 Hz波形图的局部放大图,可以更清楚的看到各通道间的相位偏移。

( 2) 采样率不一致而导致的相移问题

如前所述, 由于不同的通道采样率A /D芯片中的低通滤波器参数不一致, 这样就不可避免的造成不同的采样率通道的有不同的相移。因此,在实际系统中将采样率高的那些通道中的数据右移一段位置, 来保证所有通道的数据对齐。

在目前的系统中, 数据右移的个数是根据实际系统的情况来确定的, 是一个特例。要在理论上找到一种通用的方法, 还需要对ΔE采样芯片的低通滤器进行建立分析模型,并对该模型进行深入的分析, 来得到理论上的支持。

6 结论

本文研究了多通道异采样率信号的同步采集问题。首先介绍了多通道异采样率信号同步采集的背景和应用模型; 然后在多通道相同采样率信号同步采集的基础上,提出几种在多通道异采样率下信号同步采集的解决方案, 并对这些方案从理论上和实现上进行了较为详细的分析和比较; 讨论了其中一种方案, 并给出了相应的试验结论; 最后就本文的研究课题“多通道异采样率信号同步采集”的问题提出进一步待研究的问题。

图7 不同频率正弦波下各通道波形图

图8 10 Hz正弦波各通道采样的局部放大图

参考文献

[1 ] 李启虎. 声呐信号处理引论(第二版) . 北京: 海洋出版社, 2000.

[2 ] John Wal rod. Senso r Netw orks f or Netw ork-Centi rc Warf are Netw ork Cent ric Warfare Con ference. October 30- 31, 2000.

[3 ] Int eractiv e Circui t s and Sys t ems Ltd. Netw orks-Cen t ric Sen sor Data Acpuisi ti on. AN-SN-1. w w w. i cs-ltd. com.

[4 ] Rodger H Hosking. Cri ti cal Techniques f or High Speed A /D Converters in Real-Tim e Sys tems. Fi rs t Editi on, w w w . pen tek. com.

[5 ] Asah i Kas ei Mi cros yst em s Co. Ltd. AK5393 Enh anced Dual Bi t ΔE 96kHz 24- Bi t ADC.