����1����Ƽ1��������2**

����飺�������У�˶ʿ�о�����������Ƶͨ�š�

ͨ����ϵ�ˣ���Ƽ��Ů���߹���������Ƶͨ��. E-mail: rab1106@bupt.edu.cn

��1. �����ʵ��ѧ��Ϣ��ͨ�Ź���ѧԺ������ 100876��2. �����ʵ��ѧ�����ѧԺ������ 100876��

ժҪ����Ƶͨ���������ƶ�ͨ�š����ǵ����Ͳ��ͨ�ŵȺܶ�����Ӧ�ù㷺��ͨ���е�α���������������س��Ȳ��������������ȵ�����£�Ӧ�����Ҫ�Ա��ر���λ�ý��и���ͬ�����ڶԱ���λ��ͬ�����ٶԱ��ز���ֵ���л��֣����ݱ��ػ���ֵ�����źŵĽ�������������һ�ֻ������ṹ�ı��ر��ز����㷨�Ͷ����ӳ�����ı��ر��ظ����㷨�����Ա���ͬ���㷨�����ˣƣУǣ�ʵ�֡�

�ؼ��ʣ�����ͬ�������ر��أ����������ӳ����

��ͼ����ţ�TN911.8

Wireless spread spectrum receiver bit edge synchronization15 algorithmLi Hongjun1, Chen Ping1, Zou Yongzhong2

(1. Communication and Information Technology college,Beijing University Of Post &Telecommunication, Beijing 100876;

2. Computer colleage,Beijing University Of Post & Telecommunication, Bejing 100876)Abstract: Wireless spread spectrum communication system are widely used in many areas such as mobile communications, satellite communications and satellite navigation. when the bit length is not integer times as pseudo-random code cycle , answering machine need to find the location of the bit start . After Synchronizing with the bit position , answering machine would began to demodulate signal according to accumulating value of the bit sample point. This paper proposes a sliding window structure to capture the bit position and a delay phase-locked loop to track the bit position. This paper also introduces the implementation results of the algorithms with FPGA. Keywords: bit synchronization; bit edge; sliding window; delay phase-locked loop

0 ����

������Ƶͨ���У���α��������������س��Ȳ������������Ĺ�ϵʱ����Ҫ�ҵ�ȷ�ı�����ʼλ�ã�������ȷ���б������������֣��Ӷ���ȷ����źŵĽ���������Ҫ�������еı�����ʼλ�ý��в����ҶԱ��ص���ʼλ�ý���ʵʱ��������������ͨ���о����ջ��ָ�������ʼλ�õ������ź�������Ӱ�죬����˽�һ�����ط�Ϊ4 ��,���û������ṹԭ�����б��ز���ķ�����ͬʱ�����һ�ֶ����ӳ�����İ취��ÿһ������ʼλ�ý��м�ʱ����ͬ���������е�һ�ڽ������źŵĽ�����̣���ͼ�Լ�״̬ת��ͼ���ڶ��ڽ����˱��ز�������㷨���������϶��㷨���������ܷ�����������������һ������ͬ��ʵ�ֵİ�������������ʵ�ʵIJ��Խ����

1 ����ͬ���������

1.1 �źŴ�������

BPSK ���Ƶ�������Ƶ�źŽ��ն�[1]�����ʽ��1����ʾ��

S(t) = Am(t)C(t) cos(2π ft +ϕ ) ��1��

ʽ����m(t)�Ǵ��͵ı�����Ϣ, C(t)�Ǵ��͵�α�������Ϣ, cos(2π ft +ϕ)���ź����ز��źţ�ϕ �ǽ��ջ����źŵ��ز���λ��źŴ����ĵ�һ���ǻָ������ز�cos(2π ft)����S(t)�����±�Ƶ�������ز��źš���45 ��Ƶ����ź������ʽ��2����ʾ��

S1 (t) = Am(t)C(t) ��2��

�źŴ����ĵڶ����ָ����ص�α������ź�( ) l C t �����ҽ��н�������һ��������������֣��źű���ʽ��3��������ʾ��

ʽ��3����T ��ָһ�����صij�����ʱ�䳤�ȣ� 250 S (t)�Ľ����һ�������ڻ���ֵ��t0��ָһ�����ص���ʼ����λ�á�������о������Ǹ���2S (t)�Ļ���ֵ���������жϱ�����Ϣ�������еĹؼ��������ȷ�ҵ�����t0��

1.2 ����ͬ�����̴�����ͼ

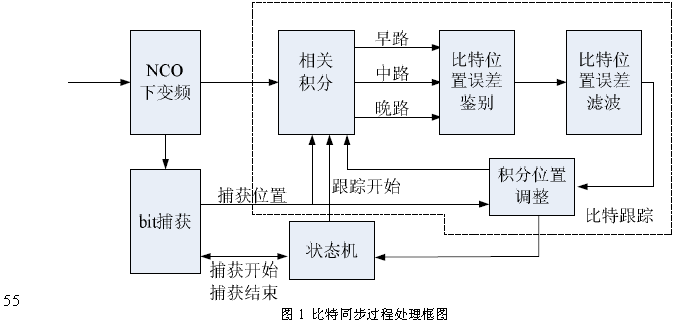

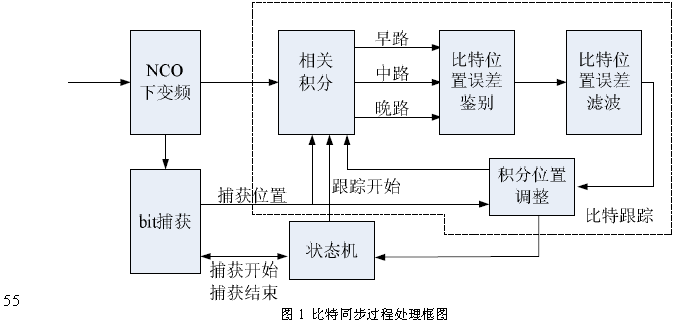

Ϊ��ȷ�ҵ�t0�������㷨�Ŀ�ͼ��ͼ1 ��ʾ��

�����㷨����а����±�Ƶ������λ�ò�����λ�ø��ٺ�״̬���IJ��֡����б��������ַ�Ϊ��������ػ��֡�������ʼλ����������������λ������˲����Լ�����λ�������IJ��֡�״̬�����������ݴ����Ŀ��Ʋ��֣��������������л����Ⱥʹ���ִ�С�

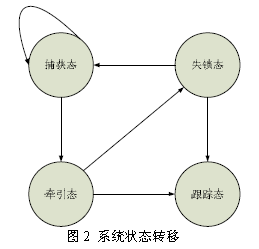

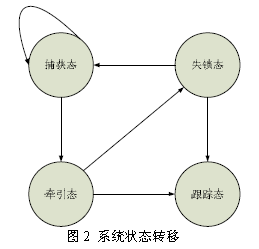

״̬����״̬ת��ͼ[2]��ͼ2 ��ʾ��

����ͬ���������ְ�������״̬������̬��ǣ��̬������̬��ʧ��̬���ڲ���̬�ڼ䣬��Ҫ��ɶԱ��س�ʼλ�õĴ�Լ���ƣ�����ƫ����±0.125 �����س������ڣ���ǣ��̬�ڼ䣬��Ҫ��ɽ�������ʼλ���ɲ�����Ĵ���λ��ǣ����ȷ��λ�ã�ƫ����±0.125 �����س��Ƚ��䵽±0.01 �����س��ȷ�Χ���ڣ�����̬��ɶ���ʼ����λ�õļ�ʱ����ͬ��������ȷ�ı�����ʼλ�ñ�־�źţ���������ʼλ��ʧͬ��֮�����ʧ��̬����һ��״̬���� ת��������̬�����½��б���λ�õ�ͬ����

����ϵͳ��״̬ת�ƶ���״̬�������жϺͿ��ơ���ϵͳ�տ�ʼ����ʱ�ᴦ�ڲ���̬���������ɹ��ͻ����ǣ��̬������������б���λ�ò���ϵͳ����ǣ��̬�ὥ����������λ��֮��������̬�����û���������������ǣ��̬������100 ��������ת��Ϊʧ��̬������ͬ�����������̬֮����ͬ�����̽������������������ֱ���λ��ʧͬ���ͻ����ʧ��̬������ͬ����

2 ����ͬ���㷨

2.1 ���ػ���ֵ�����λ�õĹ�ϵ

���ݽ�������У����ݱ��ػ���ֵ�ķ����жϴ�����Ϣ�����ػ���ֵ���ų������Ǵ�����������ص�ֱ�۷�ӳ�������ػ��ֽ��ֱ�������λ���кܴ��ϵ[3]����ͼ3 ��ʾ��

���س���ΪT����û��������Ӱ���£����ػ���ֵ��AT ��−AT ��������λ�ô���Δtƫ��ʱ�����ػ���ֵ��ʧ2AΔt�����ػ���ֵ��ΪA(T − 2Δt)�����ڱ��ػ���λ�ò�ȷ

�����ϵͳ��������Ӱ��ܴ�[4]��

2.2 �������ṹ�ı��ز����㷨

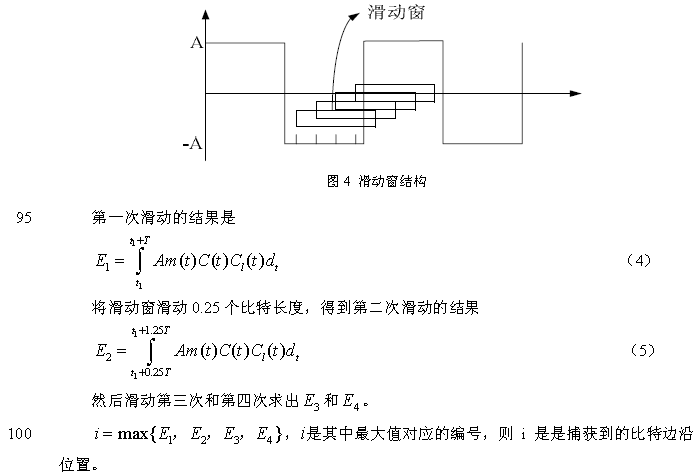

���ز����㷨���û������ṹ����һ�����ط�Ϊ�ĶΣ�Ȼ������һ������������������

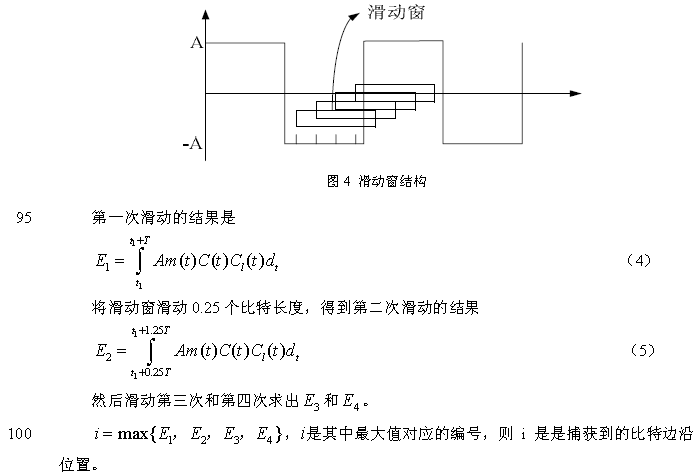

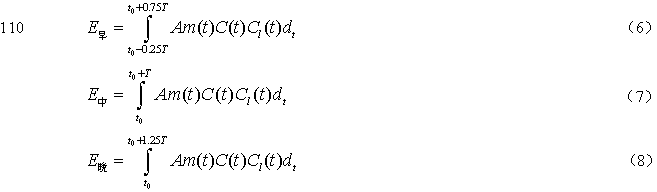

����Ϊһ�����صij��ȣ�������������㻬����֮ǰ����ÿһ�ε���㣬֮��۲��ڻ������µı��ػ���ֵ�������ij�ε���ʼλ�û���ֵ���˵�����ڻ��������������ʼλ���������������֪���ز��ִ��ڵ�ƫ��Ϊ±0.125 �����س������ڡ�����ԭ����ͼ4 ��ʾ��

2.3 �ӳ�����ı��ظ����㷨

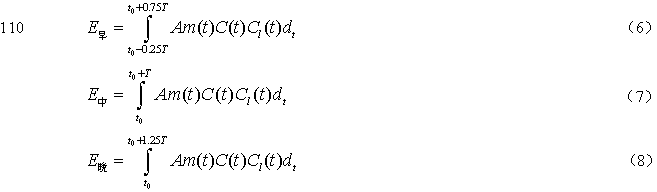

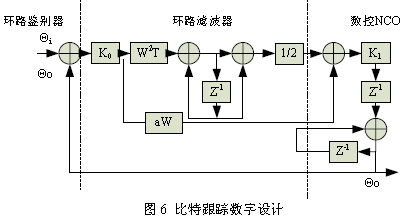

������ʼλ�ò������֮�������������٣���ʱ����λ�û�����0.125 �����س��ȵ�ƫ����ٽ����ڴ˻������ҵ�ȷ�ı�����ʼ����λ�á� ������ʼλ�ø�������Ҫ���������DZ���λ�ü�����������λ���˲���������NCO������λ�ü�������Ҫ�������ǰ������Ƶ�ջ��ָ��ı��ر����������źŵı��ر���֮���IJ�ࡣ����λ���˲������������Ľ����ȥ������Ȼ�����˲����������·��������·���ǵ�����������NCO ��ֵ��ʹ���ָ��ı���λ�ð����˲��Ľ�����б仯���ڱ���λ�ü���������Ҫ�����硢�С���·����ֵ�ֱ��ǣ�

�� 0 t �ǵ�ǰȷ���ı�����ʼλ�á���·����·�ֱ�����0.25 �����س��Ⱥ���0.25 �����س�����Ϊ���Ļ��ֽ��������ı���ƫ���㷨���¡�

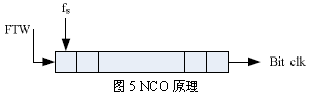

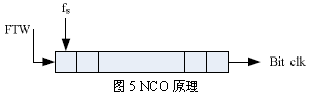

�ڲ���FPGAʵ��ʱ������ͬ���˲������ö���IIR �˲���, �˲�����Ҫѡ�ú��ʵĴ�������������Сʱ���п����˳�һ���������źţ���ɽ��ջ��Ķ�̬Ч�����ã�����·��������ʱ���п��ܽ��������������ϵͳ����ɱ���ͬ������ȷ[5]�������Ҫ���ݷ�������ʵ�ʻ���ȷ��������NCO ����16 ���ص��ۼ���������д��ı������ʿ�����FTW �IJ�ͬ�������ı���ʱ������Ҳ�ͬ������ʱ�ӵ�һ�����ھ���һ�����صij��ȣ�������ʱ������ȫ���롣����NCO �Ľṹʾ��ͼ������ʾ��

FTW ����NCO ����д��������֣�fs���ۼ�FTW��Ƶ�ʣ�Bit_clk���±�����ʼ��־�źţ�����NCO ÿ�ۼ����һ��Bit_clk ��־�ͻ����һ��ʱ�ӵ���Ч�źš���˿��Եõ�ʽ��13����

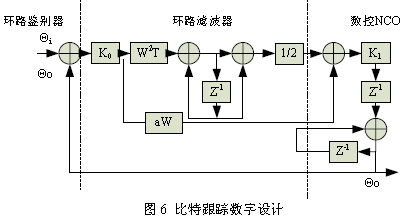

ͨ������FTW ���Կ���Bit_clk �������ٶȣ��������ƽ��ջ��ı��ر������źŵı������ر���ͬ�����������ظ��ٲ��ֵ�������ƽṹ��ͼ6 ��ʾ��

W ���˲�����ԲƵ��,T�Ǹ��ٻ�·�ĵ���ʱ�䣬a ���˲�����ϵ��[2]��

3 �㷨 FPGA ʵ��

���õڶ����������ܿ�ͼ�����ֽṹ����������Ϊ3.069MHz�������ڳ�����1023�����ش�������Ϊ4K��ͳʱ�ӹ�����47M�����յ�����Ƶ�ź�180M �Ľ��ջ��ź�ͬ��ϵͳ������FPGA ʵ�֡�ϵͳ���õĻ�·����ʱ��Ϊһ�����صij���0.25ms�����ڱ���ͬ��������ͬ������ͬ�����Ӱ��ģ�����ͬ�����������ֺ��롢�ز���ͬ�������ۺ���һ��������ԡ����Գ���Ϊ���źŹ���-123dBm���źŵĶ�̬Ч����±2.5KHz ���ڣ��ź�Ƶƫ±90KHz���ڡ�ϵͳ�ɹ�ͬ���ĸ����ܹ��ﵽ95%���ϣ�����ϵͳ����ȫͬ��ʱ����5S ���ڡ�

4 ����

���ĸ�������������Ƶͨ��ϵͳ�У�������ʼλ�õľ�ȷͬ����һ�ֹ���ʵ�ַ��������ر���ͬ���Խ���dz���Ҫ�����������ʼλ��û��ͬ�������ϵͳ�ز�ͬ����α��ͬ�������������ֱ��Ӱ�졣���������һ��4 �λ������ṹ�ı���λ�ò����㷨�Ͷ����ӳ��������ı���λ�ø����㷨����ϵͳ���ر���ͬ��������FPGA �ж��㷨������ʵ�֣��źŽ��������յIJ��Խ��֤������ͬ���㷨���зdz��õ����ܡ�

[�����] (References)

[1] �ܾ��� ���� ������ ��ΰ��.ͨ��ԭ��[M].�����������ʵ��ѧ�����磬2006.

[2] л��.GPS ԭ������ջ����[M].���������ӹ�ҵ�����磬2009.

[3] John G.Proakis , Masoud Salehi.Communication Systems Engineering[M].Beijing:Publishing House of Electronics Industry,2004.

[4] Simon Haykin,Michael Moher.Modern Wireless Communication[M].Beijing:Publishing House of Eletronics Industry,2006.

[5] ����.����ж���·�˲��������[J].���,2011,(5).