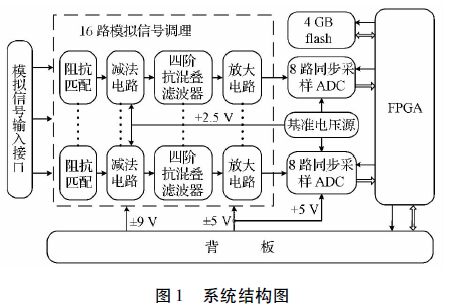

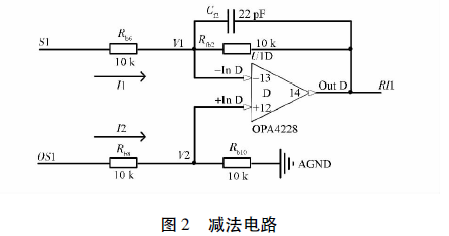

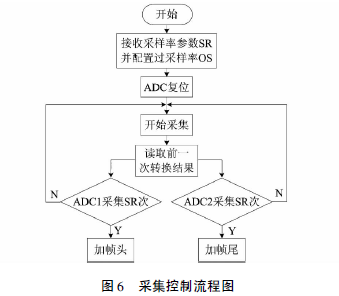

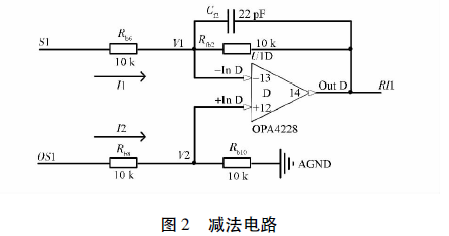

本设计中要将0 ~ 5 V 的输入信号调理到- 5 ~+ 5 V 的ADC 模拟输入范围内,采用的方法为: 先使输入信号经过减法电路减去2. 5 V,再经过一个增益为2 的放大电路。从电路结构上看,减法电路是反相输入和同相输入相结合的放大电路[4],如图2 所示。利用虚短和虚断的概念可得到式( 1) ; 如果所选电阻满足Rb6 = Rfb2 = Rb8 = Rb10,式( 1) 可以简化为式( 2) ,此时减法电路的增益为1。

图2 中所有电阻选用10 kΩ。当Vos1 = 0 V 时,I2 = 0. 25 mA,即单路减法电路最大需要0. 25 mA 的驱动电流,所以16 路最大需要4 mA。

2. 1. 3 抗混叠滤波电路设计

抗混叠滤波的实质是低通滤波,其作用是滤除被测信号中可能会折叠到低频段的高频成分,防止造成假频干扰。本设计中,ADC 的采样率是可以变化的,这给确定抗混叠滤波器的截止频率造成了困难,截止频率太小会使通过的信号失真,而截止频率太大又失去了低通滤波的意义,最好的方法是截止频率能随着采样率的变化自动调整。设计中选用了一阶RC 滤波器,其截止频率接近于LTC1068的截止频率[4],如图3 所示: 取Rff5 = 1 kΩ,Cff5 = 10nF。

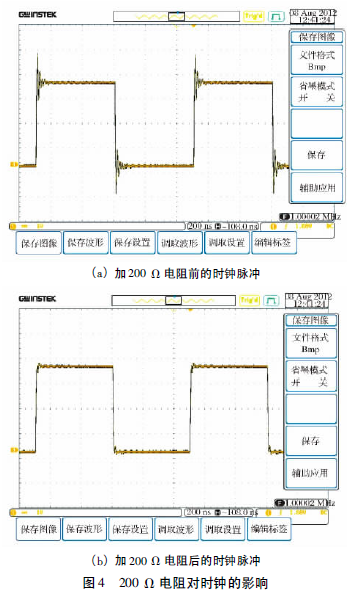

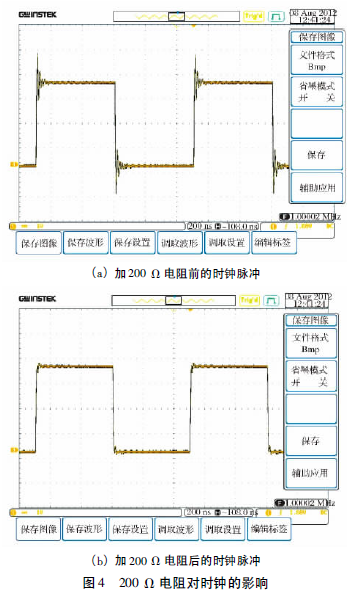

在开关电容滤波器内部,由输入时钟控制的MOS 开关高速切换,会对输出模拟信号产生馈通效应,因此在滤波器输出端也要加RC 低通滤波器来最大限度降低时钟馈通引入的噪声。如图3 中Rff51、Cff51所示。FPGA 产生的方波脉冲直接输入到LTC1068 时钟管脚时会产生较大的过冲和下冲,如图4( a) 所示; 在时钟管脚上串联一个200 Ω 电阻后,时钟线上的高频成份明显被滤除,时钟边沿的陡峭程度降低,过冲也随之消失,如图4( b) 所示。其中图中Y 轴方向每一大格代表1 V,X 轴方向每一大格代表200 ns。

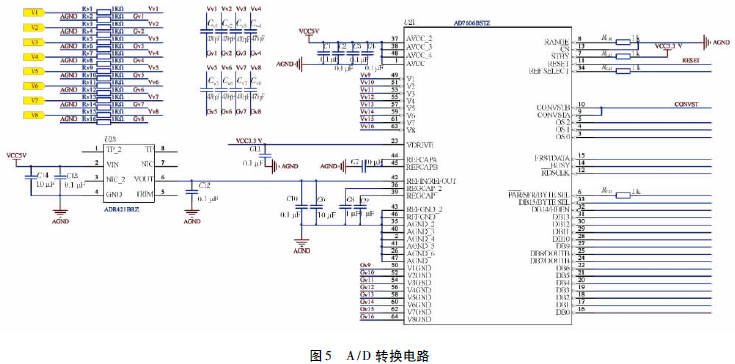

2. 2 A/D 转换电路的设计

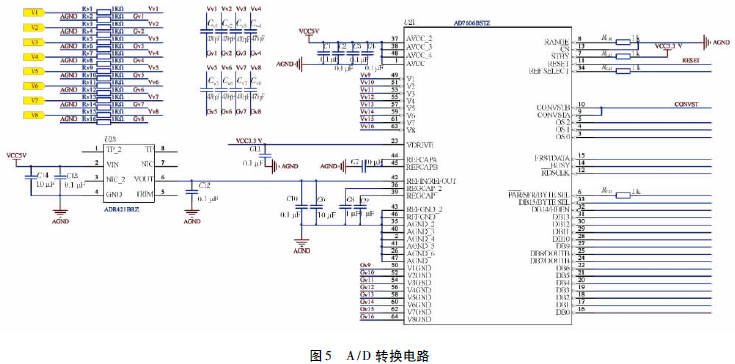

设计中选用了8 通道AD7606 作为本系统采集芯片,尽管AD7606 的内部箝位保护电路允许输入过压达到± 16. 5 V,但瞬时电压可能超过± 16. 5 V导致箝位电路开启而损坏器件。因此在模拟输入通道上应该放置一个串联电阻,以将超过± 16. 5 V的电流限制在± 10 mA 以下。设计中选用了1 kΩ的电阻,如图5 中RV1所示。因为模拟输入通道Vx上串联了一个电阻,每个模拟输入对应的VxGND 上也应该串联一个与之相等的电阻以防止出现失调误差,如图5 中Rv2所示。AD7606 支持三种数字接口模式: 高速串行模式、并行字节( 8 bit) 模式和并行( 16 bit) 模式,所需接口模式可以由PAR /SER/BYTE 和BYTE SEL 两个管脚来选择。考虑到接插件的接线端子数和PCB 空间都比较紧张,本设计选用了并行字节模式,所有通道的A/D 转换结果( 16位) 分两次8 位读出,先读高8 位,后读低8 位。通道间按升序逐个读出,即第一次读出的是通道1 的高8 位,最后一次读出的是通道8 的低8 位。并行字节模式比并行模式节省空间,比高速串行模式节省时间。

3 FPGA 逻辑时序设计

3. 1 通信协议设计

设计通信协议是为了保证整个测试系统有条不紊地协同工作,本文主要详细介绍主控制卡与采集存储卡之间的通信协议,不论是主控制卡向采集存储卡下发数据,还是采集存储卡向主控制卡上传数据,也不论传送的是地址、命令还是数据,主控制卡与采集存储卡之间都是以9 位二进制数的形式通信的,如表1 所示,其中D8 是标志位,‘0’代表数据,‘1’代表地址或命令,到底是地址还是命令还要看D7,D7 的‘0’代表地址,‘1’代表命令。传送地址时,D6 ~ D2 代表测试记录仪的地址,D1 ~ D0 代表一台测试记录仪中采集存储卡的地址,D0 的‘0’代表选中第一块采集存储卡,‘1’代表选中第二块采集存储卡,而当D1 为‘1’时,无论D0 是什么,两块采集存储卡都被选中。采集存储卡将D1 ~ D0 的值与自己的实际地址相比较,来判断是不是给自己发的命令。

传送命令时,D6 ~ D0 代表命令代码,命令代码与具体内容的对应关系如表2 所示。数据分为采样率参数和编帧之后的数据,前者由主控制卡下发给采集存储卡,后者由采集存储卡上传至主控制卡。如果数据是前者,D7 ~ D4 代表ADC2( 9 ~ 16 路) 的采样率,D3 ~ D0 代表ADC1( 1 ~ 8 路) 的采样率,采样率参数与实际采样率的对应关系如表2 所示; 如果数据是后者,D7 ~ D0 代表AD7606 实际采集的数字量或附加的帧标志,当且仅当上传帧结束标志( 帧尾) 时D8 为‘1’,以告知主控制卡已读完一帧数据。

3. 2 采集控制模块

一块采集存储卡上有两片AD7606,其中ADC1采集1 ~ 8 路模拟信号,ADC2 采集9 ~ 16 路模拟信号。由于两片AD7606 的采样率可能不同,因此它们的CONVST( 采样脉冲输入) 、RD /SCLK( 读数时钟) 和DB7 ~ DB0( 数据输出端口) 在硬件上应该相互独立,采集控制逻辑也不能混在一起; 但是当两片AD7606 的采样率相同时,只有它们的转换脉冲同步才能保证所有通道间同步采样。因此设计中用同一个时钟驱动两个不同状态机来分别控制两片AD7606 的采样、读数,这样,在相同时间内两个状态机执行的状态数是相同的,也就是说同一时刻下采样率相同的两片AD7606 几乎处于转换周期的同一阶段[5]。

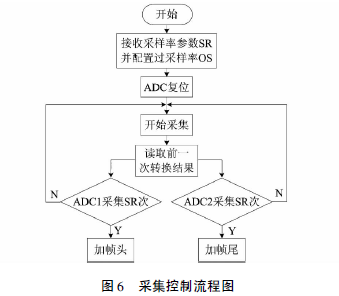

FPGA 上电后的初始状态会自动配置AD7606的工作模式,包括选择接口模式、选择内/外参考电压等,AD7606 开始采集前必须复位一下才能确保在正确的模式下工作。图6 给出了采集控制的流程图。

如图6 所示,开始采集前,采集控制模块会收到各片AD7606 的采样率参数,根据这个参数即可以配置过采样率。过采样率设置为4 时,可选择的采样率最大值刚好为50 ksps,但如果加上转换完成后的读数时间,实际采样率就达不到50 ksps,所以设计中选择了在转换过程中读数,只不过读出的是前一次A/D 转换的结果。

如图6 所示,每当ADC1 采集达到一帧数据量时都需要加帧头“EB + 90 + 卡地址+ 采样率参数”,其中,“卡地址”用于标识数据帧的归属,“采样率参数”与帧的数据量有关。同理每当ADC2 采集达到一帧数据量时都需要加帧尾“14 h”,作为一帧数据结束的标志。

4 性能测试

4. 1 减法电路测试

从减法电路的同相输入端输入如图7( a) 所示的正弦波,频率为10 kHz,峰峰值为5 V,反相输入端接到ADR421 的输出端,图7( a) 中“ ”为0 V 电压基准线。经过减法电路后的输出如图7( b) 所示。

对比图7( a) 和图7( b) 可以看出: 经过减法电路后,0~ 5 V 的正弦信号被“减去”2. 5 V,成为-2. 5 ~ + 2. 5 V 的正弦信号,而频率没有变化。其中图中Y 轴方向每一大格代表1 V,X 轴方向每一大格代表50 μs。

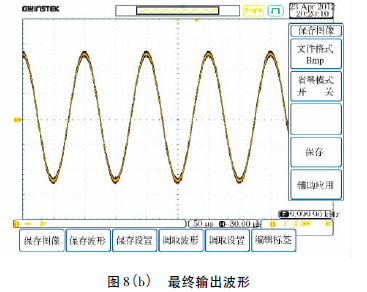

4. 2 整个调理电路测试

从调理滤波电路的最前端输入如图8( a) 所示的10kHz 正弦信号,峰峰值为5 V,相当于0 ~ 5 V输入,经过跟随电路、减法电路、滤波电路、放大电路后最终输出- 5 V ~ + 5 V 的正弦信号,波形如图8( b) 所示。其中图中Y 轴方向每一大格代表2 V,X 轴方向每一大格代表50 μs。

4. 3 功能测试

输入一个3. 08Vpp的正弦波,在计算机软件中设置ADC1 和ADC2 的采样率分别是1 ksps 和5 ksps,截取两段采集得到的数据如图9 所示。